Battery is the most extensive use power supply in most applications, including electronic devices (mobile phone, wearable devices, etc.), automotive infotainment and start-stop system[1-2]. Battery voltage can be either greater or lower than the system operation voltage no matter it is charged or discharged. Thus, the implementation of non-inverting buck-boost converters is critical for regulating purpose. Compared with Sepic, Zeta and Flyback, four-switch buck-boost has much lower switch stress and magnetic element power loss, resulting in better EMI performance and higher power density. The traditional non-inverting buck-boost employs four switches with three-mode control to realize the up-down transition. However, since the hysteresis ΔV is introduced to avoid the fluctuation of the duty cycles, the line regulation performs not good enough when input voltage is close to output voltage[3]. Even with the compensation technique[4] or extra circuit like PLL[5], the dead zone still exists and the output voltage drops as the input voltage changes. The hybrid feed-forward control scheme[6-7] improves the line transient performance but needs input voltage sensing, one more dynamic sawtooth generator[8] and PWM comparator, which together make the system control more complicated[9]. Although hysteresis control could improve the efficiency in light load and load step response, the transition between hysteresis mode and PWM mode is not smooth or accurate due to the variation of external component parameters. The tradition hysteresis mode relies on the two non-overlap thresholds ILH (load current from PWM to hysteresis) and ILP (load current from hysteresis to PWM)[10]. The buck converter usually senses the inductor current as the load current and makes the decision by comparing with a reference current threshold. However, the inductor current of boost and buck-boost is related to the Vin and Vo. This paper proposes a constant inductor current control (CICC) method to make the operation mode transition smooth between hysteresis control mode and PWM control mode. Compared with the fixed transition current threshold, the CICC scheme decouples from the input and output voltage change and the parameter variation of external components.

In this paper, an inductor current slope control (ICSC) method is proposed to transit the operation mode between buck and boost in one switching cycle automatically so that it can mitigate both overshoot and undershoot of the output voltage when the input voltage changes.

1 System Architecture

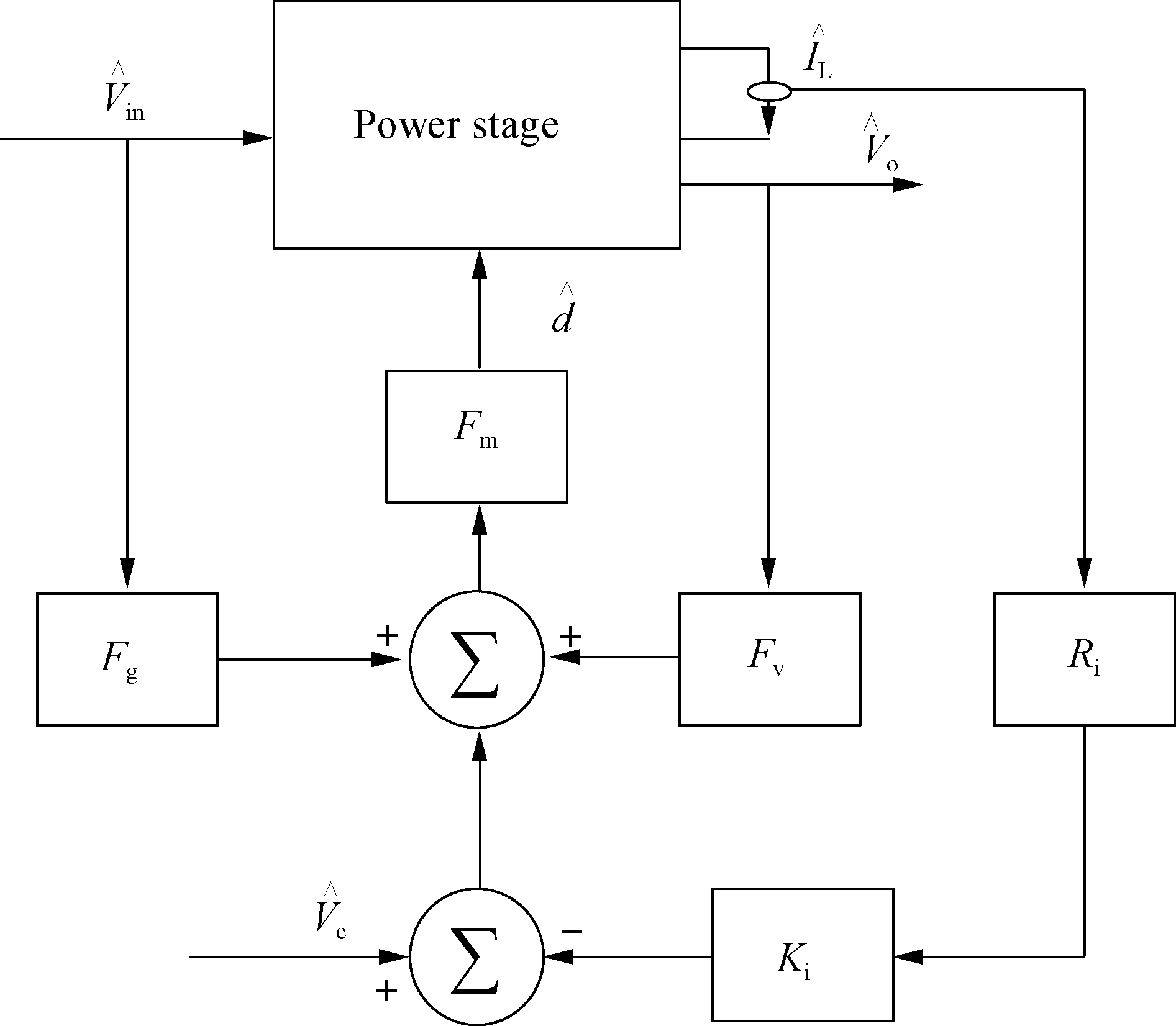

The proposed buck-boost loop control architecture is composed of the hysteresis control loop and PWM control loop shown as Fig.1. The hysteresis control loop is effective during light load while the converter transits to PWM control loop when the load increases. In hysteresis loop control, the CICC control block makes inductor current (IL) operate between the peak current limit (Ip) and the zero current (IZC) until the output voltage (Vo) exceeds the rising threshold of the feedback hysteresis comparator (FHC). Then the converter works from the alive state to the sleep state, dramatically saving the controller loss and switching loss, and obviously improving the efficiency in light load condition. With the average inductor current ramping up, the valley inductor current increases gradually more than the zero current (IZC), leading to the converter transition from hysteresis mode to PWM mode. The CICC is proposed to make the peak to valley inductor current operate with a constant value as Ip, so that the control scheme can easily implement the smooth transition between hysteresis control loop and PWM control loop. The efficiency dip is eliminated at the mode transition point, compared with the traditional fixed inductor current transition threshold.

Fig.1 The novel buck-boost control diagram

Both in hysteresis and PWM control, ICSC block senses IL. With a given inductor, the slope of IL is in proportion to the voltage across the inductor. (Vin-Vo)/L is the common coefficient in buck-boost mode so that it can be a uniform input as the current slope comparator which determines the boost or buck mode in one switching cycle. ICSC can greatly improve the line regulation performance and improve the efficiency when the Vin is close to Vo.

2 System Implementation

2.1 Inductor current slope control (ICSC)

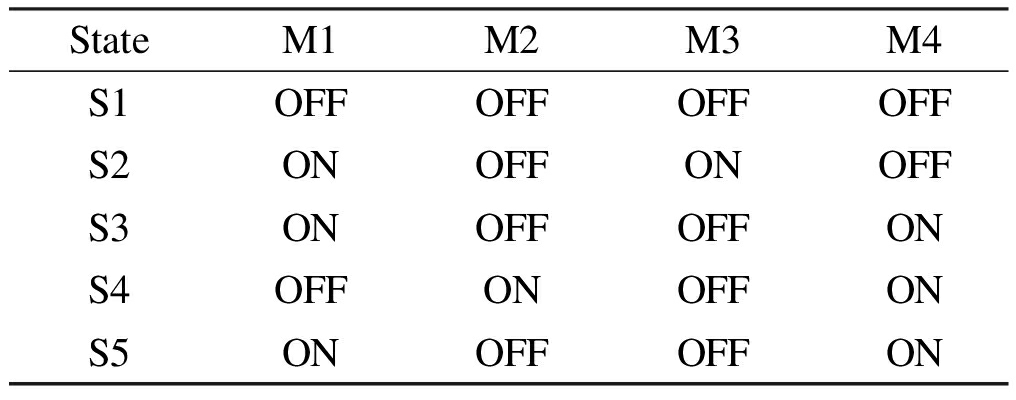

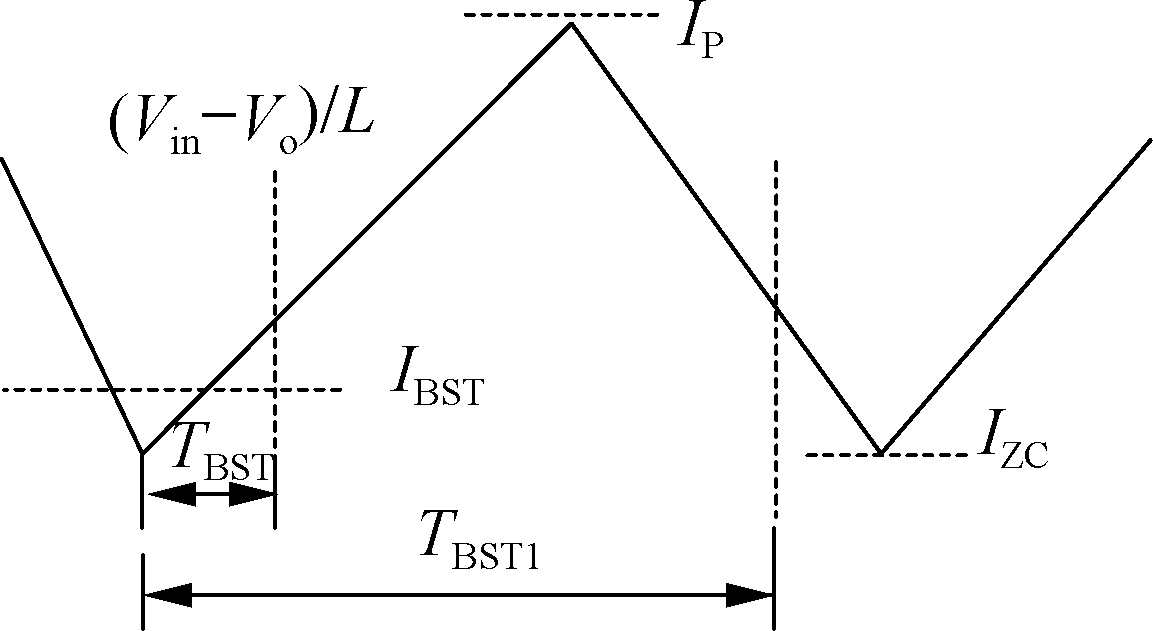

The state machine transition diagram of Fig.2 shows the operation principle of ICSC. At the initial state, assuming that Vo is greater than the reference of the feedback hysteresis comparator (FHC), the converter is operating in the sleep state S1 with all switches off which are shown in Tab.1. When the output signal of FHC turns to low, the converter transits to buck mode S3, in which M1 and M4 are turned on, if Vin is greater than Vo. When IL exceeds Ip (PK=1), the converter transits to mode S4, in which M2 and M4 are turned on. Until IL is equal to the zero current (ZC=1), the converter transits back to mode S3. As long as the FHC and CBST keep low, IL ramps up and down between zero current (IZC) and Ip. The CBST is the output signal of the boost mode comparator with two inputs as of inductor current and boost mode current threshold IBST, as shown in Fig.3. When VFB is higher than reference voltage VREF_HYS, FHC goes high and the converter transits back to the sleep state S1.

When Vin becomes lower than Vo in S1 or S4 under buck mode, the converter changes to boost mode immediately in state S3 if only IL is lower than the boost mode current threshold IBST at the delay TBST, since the rising slope of IL is proportional to Vin-Vo and can be inferred as the Vin and Vo relative level. When the Vin turns lower than Vo after the delay TBST but before IL hits Ip, the extra check at delay TBST1 is to assure that the converter changes to boost mode. At delay TBST1, if IL is still lower than Ip, the comparator output CBST1 transits to high and M1 is turned off. The converter changes to boost mode in the next switching cycle.

Fig.2 ICSC operation state machine

Tab.1 ICSC control scheme

StateM1M2M3M4ModeS1OFFOFFOFFOFFSleepS2ONOFFONOFFBoostS3ONOFFOFFONBuckS4OFFONOFFONBuckS5ONOFFOFFONBoost

(a)

(a)

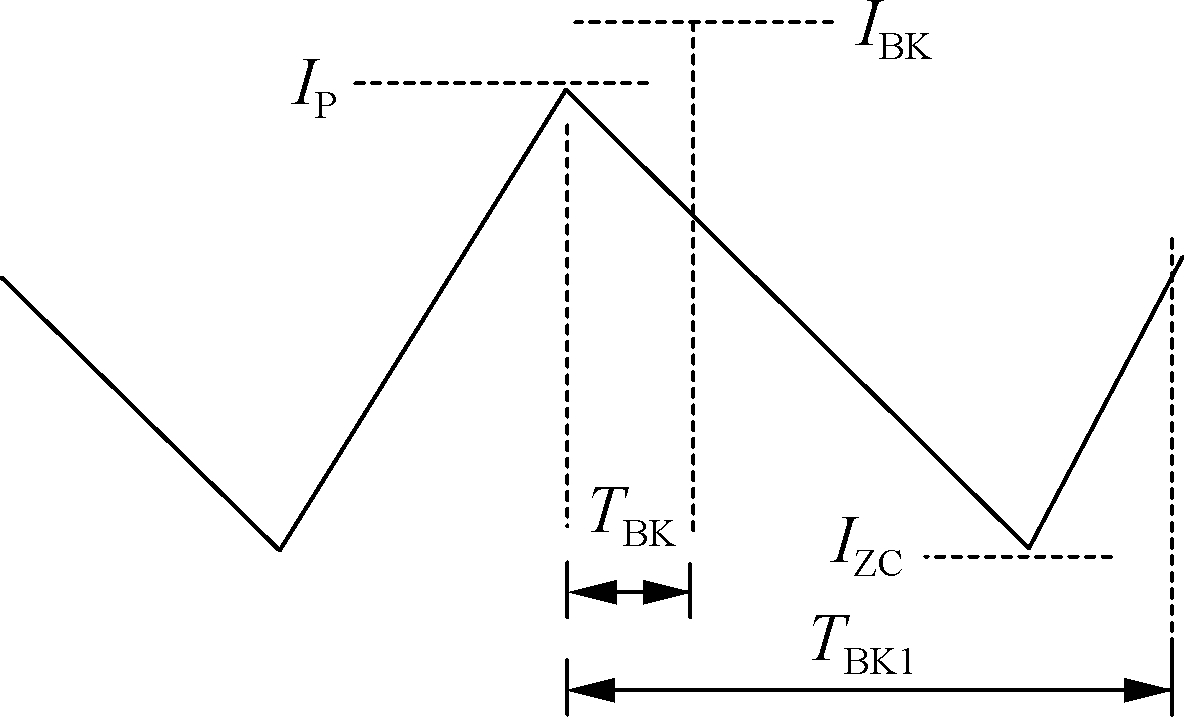

(b)Fig.3 Mode transition of inductor slope control. (a) Buck mode; (b) Boost mode

Under boost mode, the converter operates between S2 and S5 as IL ramps up and down between the peak current Ip and zero current (IZC), if only FHC and CBK keep low. CBK is the output of the buck mode comparator, with two inputs as of the inductor current IL and the buck mode current threshold IBK. If Vin becomes higher than Vo in S1 or S2, it transits to the buck mode immediately in state S5 when IL is higher than IBK at the delay TBK since the falling slope of IL is proportional to Vo-Vin and can be inferred as the Vin and Vo relative level. If Vin becomes higher than Vo after the delay TBK but before IL hits IZC, the extra check at delay TBK1 is to assure that the converter changes to buck mode as well. At delay TBK1, if IL is still higher than IZC, the comparator output CBK1 transits to high and M4 is turned off. When VFB is higher than the reference voltage VREF_HYS, FHC goes high and the converter transits back to the sleep state S1.

Based on the control scheme analysis, these transitions of the operation mode are all completed in one switching cycle with ICSC control. Furthermore, Vo is charged up quickly and the converter goes to sleep state automatically as the IL slope is flat and the Ip is much larger than the load current. Therefore, compared with the conventional buck-boost without operation mode detection, there is no efficiency degraded when Vin is close to Vo.

The mode transition threshold of Vin and Vo level can be expressed as

(1)

(2)

As voltage drops in M1~M4, it is necessary to set the mode transition threshold for Vin slightly higher than Vo. The boost-to-buck threshold is larger than the buck-to-boost threshold to avoid glitches during mode transitions.

2.2 Constant peak and valley inductor current control

CICC is proposed as the constant peak and valley inductor current control scheme. It is not an external component dependent control scheme that can smoothly and accurately transit between hysteresis loop and PWM loop. In order to improve the efficiency and transient performance, the hysteresis control loop is more effective with light load. The inductor current ramps up and down between Ip and zero current until Vo exceeds the hysteresis window and then the converter goes into sleep mode to reduce the switching loss and controller loss. With the increase in the load current, Vo and VFB drops gradually as the inductor current from peak to valley is constant. Meanwhile, the compensation node voltage of error amplifier increases to enlarge the load capability and PWM control loop is effective on the output regulation after 32 clock cycles. Finally, the reference voltage of hysteresis control and PWM control are adjusted simultaneously to cancel the load regulation under different control modes. Fig.4 shows the control loop transition from hysteresis to PWM.

Fig.4 Hysteresis to PWM mode transition of CICC

Similarly, the inductor current and compensation node voltage decrease as the load current decreases. The converter starts to skip switching pulses when VFB goes higher than VREF_HYS as the inductor current from peak to valley is constant. Meanwhile, the compensation node voltage of the error amplifier decreases and the hysteresis control loop is effective on the output regulation after 8 burst cycles. Finally, the reference voltage of hysteresis control and PWM control are adjusted simultaneously to cancel the load regulation under different control modes. Fig.5 shows the control loop transition from PWM to hysteresis mode.

Fig.5 PWM to hysteresis mode transition of CICC

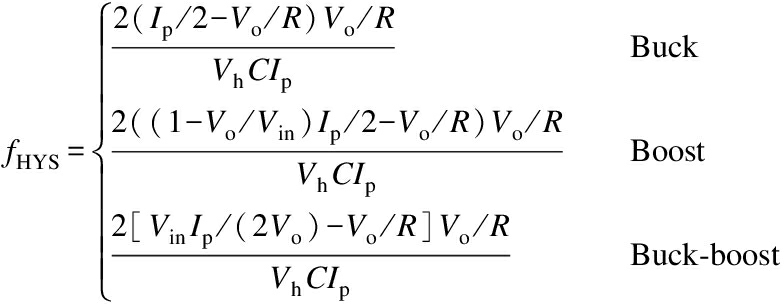

Under the hysteresis mode, the hysteresis frequency is defined by the hysteresis window Vh, peak current Ip, input voltage Vin, output voltage Vo and load R.

(3)

Under PWM mode, the switching frequency varies with peak current Ip, input voltage Vin, output voltage Vo and inductance L.

(4)

2.3 Small signal model

As the switching frequency in PWM mode varies with load current, introduce ton and ts to replace duty d as the small signal variants,

(5)

Solve it with small signal perturbation,

(6)

Take buck mode as an example to deduce the small signal model,

ton=dts

(7)

(8)

(9)

ip=〈iL〉![]() 〈iL〉

〈iL〉![]()

(10)

![]() 〈

〈![]() 〉

〉![]()

(11)

(12)

Substitute Eq.(12) to Eq.(9) and consider the current sense gain as Ri. ![]() is the output signal of the external voltage loop.

is the output signal of the external voltage loop.

(13)

According to the average model of the three-terminal device, the buck mode parameters of the CICC buck-boost can be defined as

(14)

(15)

(16)

The CICC buck mode small signal switch model is shown as Fig.6. Here Ki=1 indicates it is the average inductor current control because peak current mode has the sample and hold delay in high frequency range that is ki=He(s)=1-s/(1/Ts)+s2/(π/Ts)2. Therefore, the CICC mode is similar to the average current mode, but with better inner current loop response than peak current mode. The control-to-output transfer function is

(17)

Fig.6 Small signal model diagram of CICC buck mode

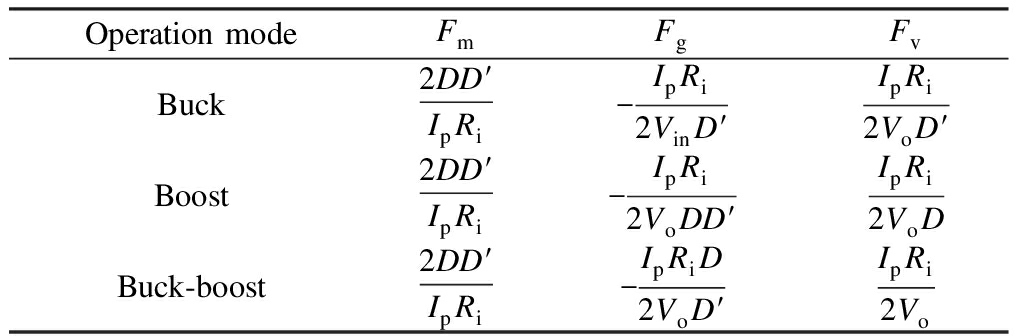

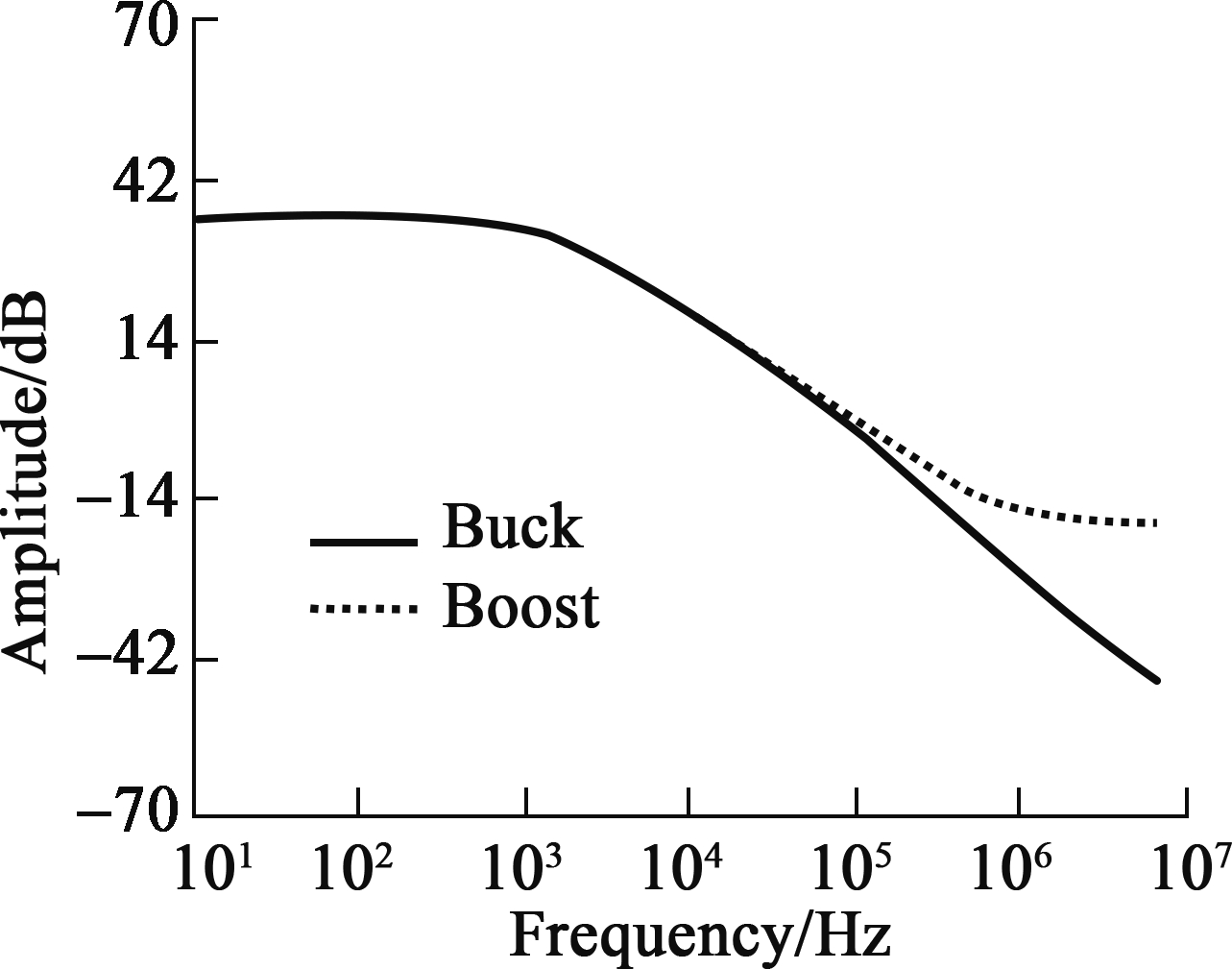

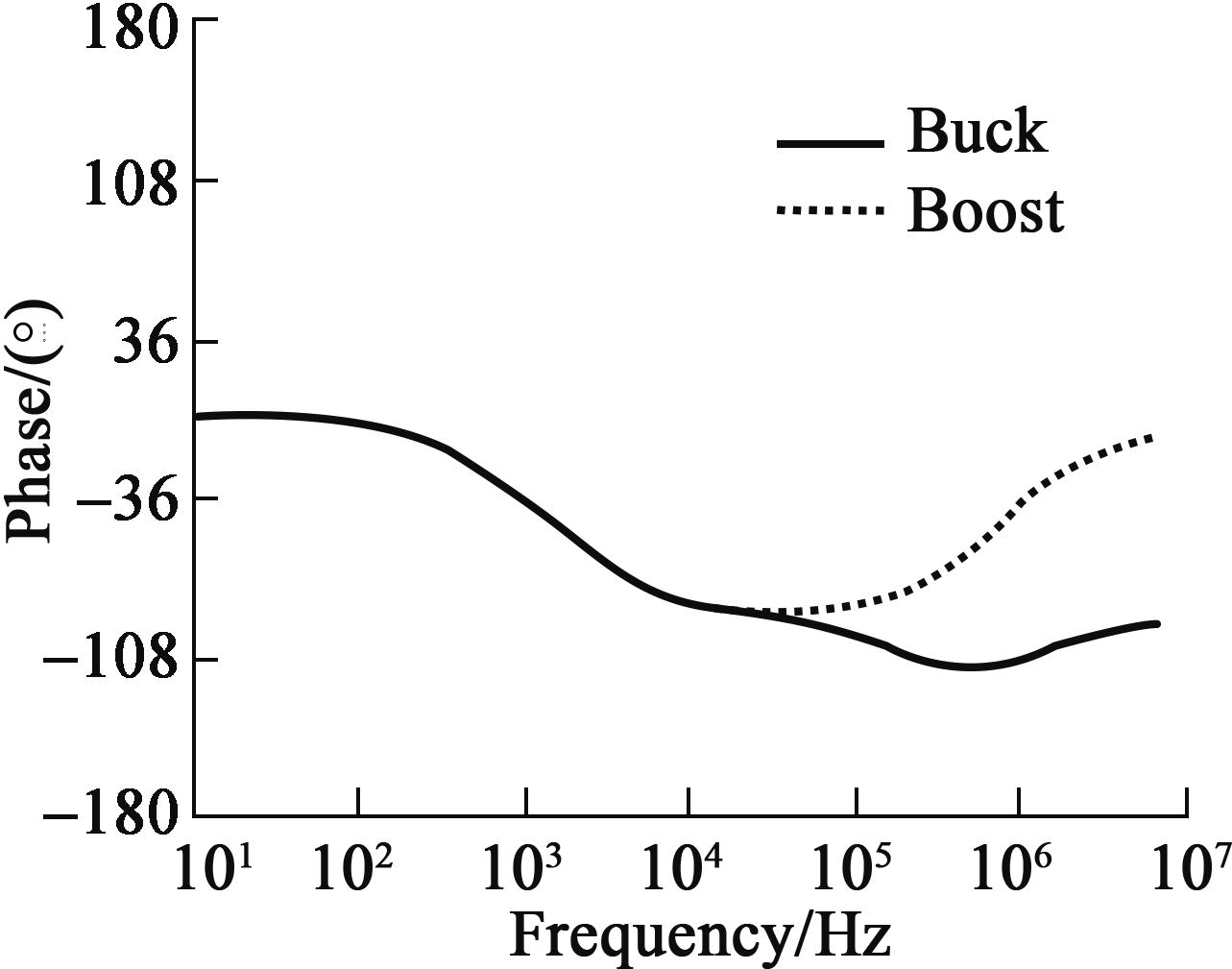

The loop modeling parameters of three operation modes are summarized in Tab.2. It is easy to extend to control-to-output transfer function of the boost and buck-boost mode. Fig.7 shows the control-to-output transfer function of buck and boost modes. These are both single pole systems so the converter keeps stable during the buck and boost mode transition.

Tab.2 Loop modeling parameter summary

Operation modeFmFgFvBuck2DD′IpRi-IpRi2VinD′IpRi2VoD′Boost2DD′IpRi-IpRi2VoDD′IpRi2VoDBuck-boost2DD′IpRi-IpRiD2VoD′IpRi2Vo

3 Experimental Results

Wide output voltage range (6-36 V) and input voltage (5-40 V) are achieved with 10 A maximum load current (2.4 A). The prototype specifications are listed in Tab.3. The typical output voltage is 12 V with 2.4 A peak to valley IL. With ICSC control, the converter is operating in buck mode with 36 V Vin, in boost mode with 6 V Vin and in buck-boost mode with 12Vin. When the voltage difference is small between Vin and Vo, switch M1 and

(a)

(b)Fig.7 Control-to-output transfer function of CICC buck-boost converter. (a) Amplitude; (b) Phase

Tab.3 Prototype specifications

ParameterValue Vin/V5-40 Vo/V6-36 Inductor/μH2.2 Output capacitor/μF100 Error amplifier gain/μS660 Current sense resistor/mΩ2 Compensation resistor/kΩ30 Compensation capacitor/nF2.2

switch M4 are almost always on during the switching phase until Vo is charged to larger than the reference rising threshold of the hysteresis comparator.

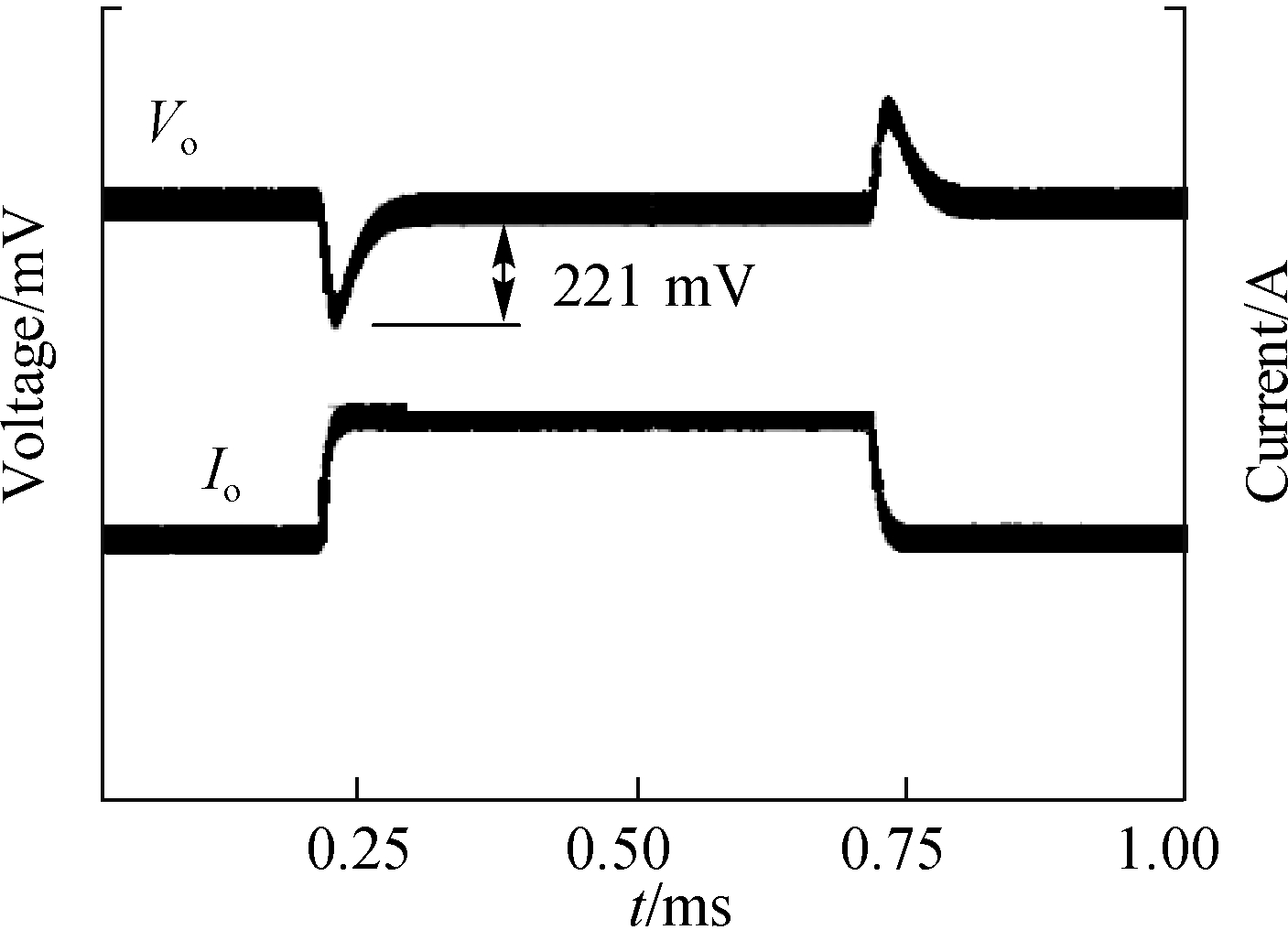

The load transient response is shown in Fig.8. The load step is 5 A, the half of the full load with 1 A/μs slew rate. The output voltage deviations are all less than 4%. Fig.9 is the line transient response. The maximum output voltage deviation is 3.8% with 7 to 18 V line transient and 0.1 V/μs slew rate.

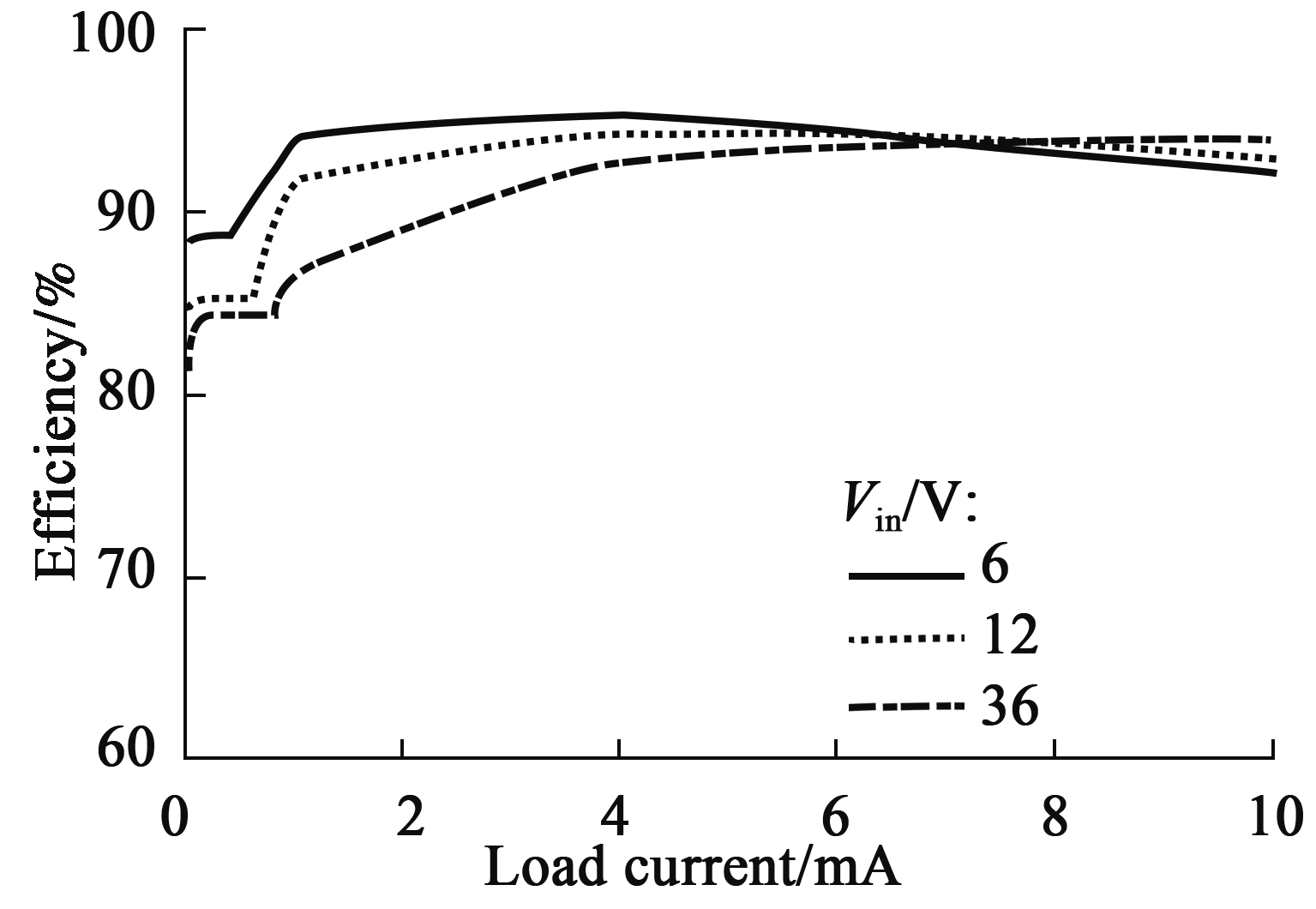

Fig.10 illustrates the conversion efficiency in different Vin. The peak efficiency reaches 95% and the full load efficiency is 94%. Furthermore, the efficiency is greater than 76% when the load current is more than above 10 mA.

4 Conclusion

1) A novel ICSC non-inverting buck-boost converter with automatic and fast buck and boost mode transition in one switching cycle is proposed in this paper. The converter avoids the output voltage fluctuation with small output ripple.

(a)

(b)

(c)Fig.8 Measured load transient performance. (a) Vin=36 V; (b) Vin=12 V; (c) Vin =6 V

Fig.9 Measured line transient performance

Fig.10 Measured efficiency

2) With the CICC control, the converter can also smoothly transit between hysteresis loop and PWM loop. The stability is verified with small signal analysis.

3) The load transient response measurement shows less than 4% deviation with half of full load step. It achieves the 95% peak efficiency and 94% efficiency at full 10 A load.

[1]Espinosa C L. Asynchronous non-inverter buck-boost DC to DC converter for battery charging in a solar MPPT system[C]//2017 IEEE URUCON Conference. Montevideo, Colombia, 2017:1-4. DOI: 10.1109/URUCON.2017.8171863.

[2]Dragoi B. On Selecting a front-end DC-DC converter for automotive applications[C]//12th IEEE International Symposium on Electronics and Telecommunications (ISETC). Timisoara, Romania, 2016: 8-20. DOI: 10.1109/ISETC.2016.7781049

[3]Sharma A, Abrishamifar A, Fazeli M. A novel peak and deep current mode control for two switches buck-boost converter[C]// 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition. Austin, TX, USA, 2008: 1021-1033. DOI:10.1109/APEC.2008.4522858.

[4]Lee Y J, Khaligh A, Emadi A. A compensation technique for smooth transitions in a noninverting buck-boost converter[J]. IEEE Transactions on Power Electronics, 2009, 24(4): 1002-1016. DOI: 10.1109/TPEL.2008.2010044.

[5]Rana N, Dey J, Banerjee S. An improved buck-boost converter suitable for PV application[C]// 2020 IEEE Calcutta Conference. Kolkata, India, 2020: 19670134. DOI: 10.1109/CALCON49167.2020.9106477.

[6]Akhilesh K, Lakshminarasamma N. Control scheme for improved efficiency in a H-bridge buck-boost converter[C]//2018 IEEE International Conference on Power Electronics, Drives and Energy Systems. Chennai, India, 2018: 18654899. DOI: 10.1109/PEDES.2018.8707633.

[7]Chen J J, Shen P N, Hwang Y S. A high efficiency positive buck-boost converter with mode-select circuit and feed-forward techniques[J]. IEEE Transactions on Power Electron, 2013, 28(9): 4240-4247. DOI: 10.1109/TPEL.2012.2223718.

[8]Veerachary M. Design and analysis of split-inductor based buck-boost converters[C]// 2019 IEEE International Symposium on Circuits and Systems. Sapporo, Japan, 2019: 18815514. DOI: 10.1109/ISCAS.2019.8702134.

[9]Soheli S N, Sarowar G, Hoque M A, et al. Design and analysis of a DC-DC buck boost converter to achieve high efficiency and low voltage gain by using buck boost topology into buck topology[C]//2018 International Conference on Advancement in Electrical and Electronic Engineering. Gazipur, Bangladesh, 2018:18471913. DOI: 10.1109/ICAEEE.2018.8643001.

[10]Liu P J, Chang C W. CCM noninverting buck-boost converter with fast duty-cycle calculation control for line transient improvement[J]. IEEE Transactions on Power Electronics, 2018, 33(6): 5097-5107. DOI: 10.1109/TPEL.2017.2734808.